Notice

Recent Posts

Recent Comments

Link

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

Tags

- C언어

- mysql

- strcat

- 정글#정글사관학교#3기#내일#기대#설렘#희망#노력

- Error Code: 1055

- HTTP

- ip

- strcpy

- SQL

- DNS

- BSD소켓

- https://firecatlibrary.tistory.com/49?category=874970

- group by

- https://coding-factory.tistory.com/641

- web-proxy lab

- TCP

Archives

- Today

- Total

매일을 설렘으로

[컴퓨터시스템] Computer structure (반효경 교수 수업) 본문

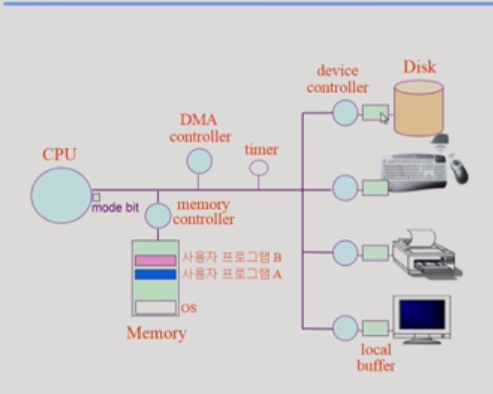

※ CPU는 메모리랑만 일하는데, 프로그램이 실행되다가 파일을 읽거나 scanf으로 읽어와야 할 일이 있을 때 CPU는 읽어 오라고 DMA controller에게 시킨다. 주변 기기들과의 의사소통을 한다.

운영체제가 timer의 도움을 받아서 프로그램들을 처리해나간다. Time sharing.

Mode bit

1 사용자 모드

2 커널 모드

- mode bit이란, 제어권이 운영체제가 가지고 있는지, 사용자 프로그램이 가지고 있는지에 대한 표시.

- mode bit이 0 경우, 운영체제가 CPU를 들고있는 것이고 모든 명령을 할 수 있는 상태 (I/O 접근까지도)

- 운영체제가 사용자프로그램에 넘겨줄 때, mode bit을 1로 변경해주고 넘겨준다.

- mode bit이 1 경우, 사용자 프로그램이 제어권을 가지고 있어, 제한된 영역만 접근할 수 있다.

- mode bit의 목적 : 사용자 프로그램의 잘못으로 초래할 수 있는 위험을 막기 위함.

Timer

정해진 시간이 흐른 뒤 운영체제에게 제어권이 넘어가도록 인터럽트 발생

- 타이머는 매 클럭 틱마다 1씩 감소 (설계시 참고)

- 타이머 값이 0이 되면 타이머 인터럽트 발생

- CPU를 특정 프로그램이 독점하는 것을 보호한다.

- Time sharing이 구현되게 한다.

I/O device controller

해당 I/O 장치 유형을 관리하는 일종의 작은 CPU

- 제어 정보를 위해 control register, status register를 가짐

- local buffer를 가짐 (일종의 data register) : data를 담은 주머니

- buffer에 data가 쌓이면 CPU interrupt가 걸려 본인의 주소로 옮겨온다. (-> 너무 자주 발생해서 CPU 제 일을 못함 그래서 DMA controller를 사용함 -> CPU와 DMA controller가 동시 접근하지 못하게 Memory controller 사용)

- I/O는 실제 device와 local buffer 사이에서 일어남

- Device controller는 I/O가 끝났을 경우 Interrupt로 CPU에게 그 사실을 알림

DMA controller

특정 하드웨어 하위 시스템이 CPU와 독립적으로 메인 시스템

메모리에 접근할 수 있게 해주는 컴퓨터 시스템의 기능이다.

- device driver (장치 구동기) : OS 코드 중 각 장치별 처리 루틴 -> software

- device controller (장치 제어기) : 각 장치를 통제하는 일종의 작은 CPU -> hardware

궁금한 점

1. DMA controller로 하위 하드웨어가 메모리에 접근이 가능한데, 위험한 건 아닌지?

-> DMA controller 작동 방식 공부

기본적으로 모든 입출력(I/O) 명령은 특권 명령이다.

입출력(I/O) 수행 과정은 어떤가?

- 시스템 콜 : 사용자 프로그램은 운영체제에게 I/O 요청

- Trap을 사용하여 인터럽트 벡터의 특정 위치로 이동

- 제어권이 인터럽트 벡터가 가리키는 인터럽트 서비스 루틴으로 이동

- 올바른 I/O요청인지 확인 후 I/O 수행

- I/O 완료 시 제어권을 시스템 콜 다음 명령으로 옮김

궁금한 점

1. Trap이 무엇인가? => 소프트웨어적으로 인터럽트를 한다. why it uses?

2. 제어권이 인터럽트 벡터가 가리키는 인터럽트 서비스 루팅으로 이동했다는 말은 무엇인가?

3. 올바른 I/O 요청이라는게 무엇인가?

인터럽트 (Interrupt)

인터럽트를 당한 시점에서 레지스터와 PC를 Save 한 후 CPU의 제어를 인터럽트 처리 루틴에 넘긴다.

- Interrupt (넓은 의미)

- Interrupt (하드웨어 인터럽트): 하드웨어가 발생시킨 인터럽트 (ex. 특정 프로그램이 독점하는 걸 방지하기 위해 사용하는 timer, 또는 키보드 사용이 끝났다는 걸 말해주기 위한 conroller 등으로 생김)

- Trap (소프트웨어 인터럽트)

- Exception : 프로그램이 오류를 범한 경우

- System call : 프로그램이 커널 함수를 호출하는 경우

- 사용자 프로그램 실행 도중에 I/O입출력을 하려면 직접 CPU를 조작할 수 없기 때문에 직접 interrupt를 하고(mode bit 1 -> 0, 의미는 CPU가 사용자 프로그램에서 OS로 사용권이 넘어감), 그리고 OS에게 system call을 한다.

인터럽트 관련 용어

1. 인터럽트 벡터 : 해당 인터럽트의 처리 루틴 주소를 가지고 있음

2. 인터럽트 처리 루틴 (=Interrupt Service Routine, 인터럽트 핸들러) : 해당 인터럽트를 처리하는 커널 함수

동기식 입출력(synchronous I/O) : I/O 요청 후 입출력 완료된 후에야 제어가 사용자 프로그램으로 넘어감

. 구현 방법 (입출력이 완료된 이후에 실행)

- I/O가 끝날 때까지 CPU를 낭비시킴

- 매시점 하나의 I/O만 일어날 수 있음

. 구현 방법2 (입출력 완료된 후 그 프로세스는 실행되지않고, 다음 프로세스로 넘어가는 방식)

- I/O가 완료될 때까지 해당 프로그램에게서 CPU를 빼앗음

- I/O 처리를 기다리는 줄에 그 프로그램을 세움

- 다른 프로그램에게 CPU를 줌

비동기식 입출력 (asynchronous I/O) : I/O가 시작된 후 입출력 작업이 끝나기를 기다리지 않고 제어가 사용자 프로그램으로 즉시 넘어감

위 두 경우 모두 I/O의 완료는 인터럽트로 알려줌

서로 다른 입출력 구조

- 오른쪽이 memory mapped I/O : 메모리 주소의 연장선으로 I/O device address를 부여함.

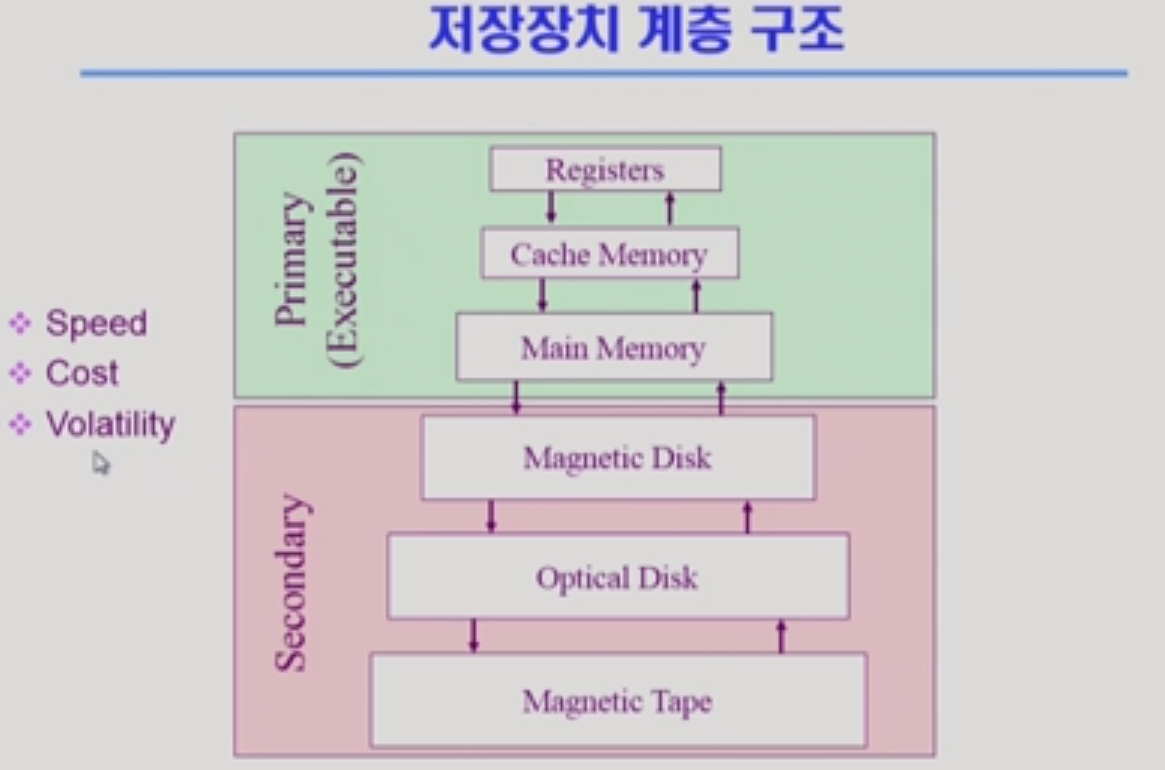

저장장치 계층 구조

- Speed/Cost : 위로 올라갈수록 빠르다.

- Volatility : Primary가 Volatility적이다. 휘발성이다.

프로그램 실행

프로그램이 실행되면 메모리에 로드되고, 프로세스마다의 독립된 가상주소 공간이 만들어진다.

2021.12.15 - [컴퓨터시스템] - [컴퓨터시스템] 가상메모리 (Virtual Memory)

[컴퓨터시스템] 가상메모리 (Virtual Memory)

목차 가상메모리란 무엇이고, 왜 필요한가 가상메모리 주소 공간 (Virtual Address Space, VAS) Stack Heap Data Code, Text 가상 메모리 (Virtual Memory) 실제 메모리 크기와 상관없이 메모리를 이용할 수 ..

beeehappy.tistory.com

함수 (Function)

- 사용자 정의 함수

- 라이브러리 함수

- 커널 함수 : 운영체제 프로그램 함수이며, 시스템 콜

사용자 정의함수에서 시스템 콜을 할 경우, 프로세스 A Address space code에서 interrupt하고 CPU제어권을 사용자에서 운영체제로 넘겨서 커널함수가 실행하게 된다.

'CS' 카테고리의 다른 글

| [컴퓨터시스템] 프로세스 생성 (Process creation) (0) | 2021.12.24 |

|---|---|

| [컴퓨터시스템] 프로세스 (반효경 수업) (0) | 2021.12.24 |

| [컴퓨터시스템] OS란 (반효경 수업) (0) | 2021.12.24 |

| [컴퓨터시스템] 가상메모리 (Virtual Memory) (0) | 2021.12.15 |